### MATRA MHS

## 29C93A

## ECMA 102/V110 Terminal Rate Adaptor Circuit (TRAC)

### Description

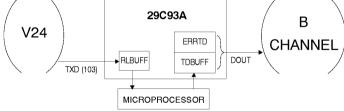

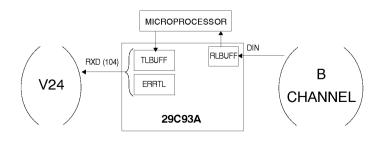

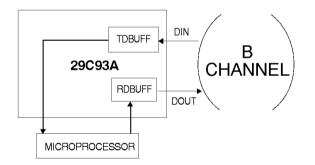

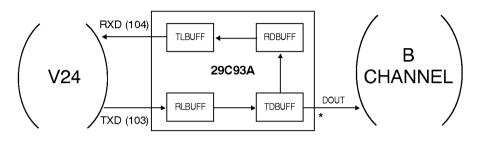

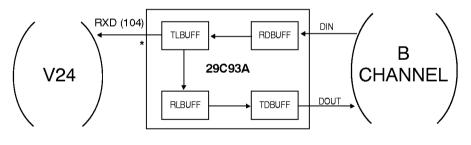

The 29C93A is a Terminal Rate Adaptor Circuit (TRAC) performing speed adaptation between synchronous/asynchronous V24 terminals through ISDN 64 kbps "B" channel.

The TRAC can be connected to "B" channel using a programmable serial bus interface SLD, IOM... Programming is made in CLKSEL register.

The Master clock signal (7 or 12 MHz) is applied to input MCLK.

In asynchronous mode it is possible to exchange data between two terminals working at different speeds but using the same intermediate rate.

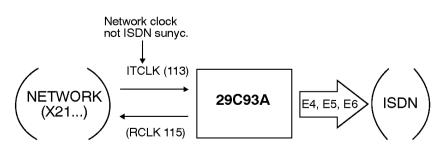

For synchronous terminals, the TRAC is able to work with network independent clocks, without addition of external circuits for phase compensation.

In X21 applications, the TRAC/V24 interface should be directly connected to the X21 controller 29C921 serial interface.

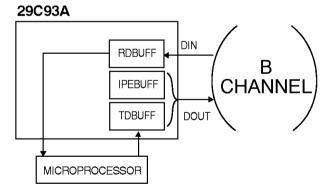

The Inband Parameters Exchange (IPE) is supported by the 29C93A. During initialization the microcontroller

sends a set-up message through the TRAC  $\mu$ P interface. Parameters exchange is achieved through"B" channel on a byte basis at 64 kbps. Distant terminal parameters are sent through parallel port and processed by the external microprocessor, using external memory for buffering.

Synchronous IPE facilities provided are : On transmit side, IPE signals (State or Command) may be sent to distant TE many times (more than 32 times as specified in ECMA123) without  $\mu$ P bus load increase (auto-repeat transmission allowed in sync. IPE). On receive side, IPE signals FF (INACTIVE), FE (IDLE), FB (FILL), ... will be filtered so that they are detected during the first reception (interrupt generation) and ignored during the following receptions.

V25 bis protocol (call establishment) is also supported in async. mode by connecting the  $\mu P$  bus to the V24 interface.

The TRAC together with ISDN layer 1/2 circuit using IOM/SLD/SSI interface provides a cost effective solution for implementation of a V24/ISDN Terminal Adaptor.

### Features

- Network independent clock supported in SYNC mode

- Rate adaptation between V24 terminal and ISDN B channel

- Full ECMA 102/V110 processing for SYNC. and ASYNC. terminals

- 50 to 57600 bps user data rates for asynchronous transmissions

- 600 to 64000 bps user data rates for synchronous transmissions

- IPE control characters processing (XSTART, FILL, OFF, IDLE...)

- "End to End" or "local" flow control capability using XON/XOFF or 105/106 circuits

- Easy interface with X21 terminals through X21 controller 29C921

- V25bis protocol compatible (call set-up through µP bus)

- In band parameter exchange (ECMA123 IPE) via µP bus

- Transparent mode capability (64 kbps)

- V24 interface

- 8 bit microprocessor interface

- Programmable serial system interface (IOM, SLD, SSI ...)

- Programmable escape character

- Power down mode

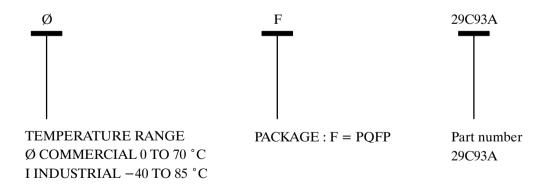

- Package = PQFP 44

### Interface

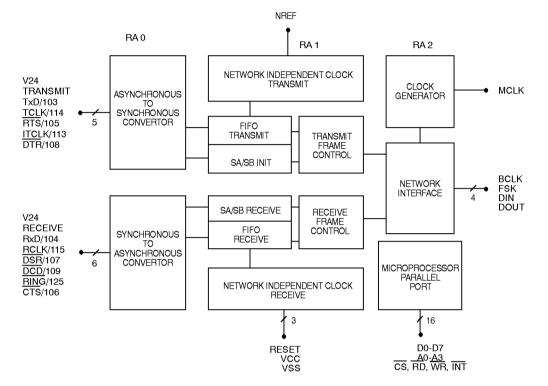

### **Block Diagram**

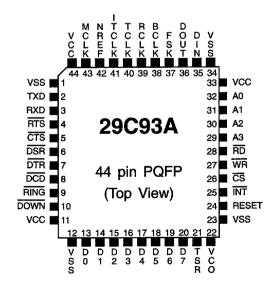

### **Pin Configuration**

### **Pin Description**

| PIN         | NAME  | FUNCTION                                      | IN/OUT |

|-------------|-------|-----------------------------------------------|--------|

| 13-20       | D0:D7 | BIDIRECTIONAL DATA BUS                        | IN/OUT |

| 29-32       | A0:A3 | REGISTER ADDRESS BUS                          | IN     |

| 26          | CS    | CHIP SELECT (ACTIVE LOW)                      | IN     |

| 28          | RD    | READ SIGNAL (ACTIVE LOW)                      | IN     |

| 27          | WR    | WRITE SIGNAL (ACTIVE LOW)                     | IN     |

| 25          | ĪNT   | INTERRUPT SIGNAL (ACTIVE LOW)                 | OUT    |

| 38          | BCLK  | SYSTEM BUS BIT CLOCK                          | IN*    |

| 43          | MCLK  | BAUD RATE MASTER CLOCK (12/7 MHz)             | IN*    |

| 42          | NREF  | NETWORK REF CLOCK (192/512/1536/2048 kHz)     | IN*    |

| 35          | DIN   | SYSTEM BUS DATA INPUT                         | IN*    |

| 36          | DOUT  | SYSTEM BUS DATA OUTPUT                        | IN/OUT |

| 37          | FSK   | SYSTEM BUS FRAME SYNC (8 kHz)                 | IN*    |

| 41          | ITCLK | V24 (113) CIRCUIT (NETWORK INDEP. CLOCK)      | IN*    |

| 40          | TCLK  | V24 (114) CIRCUIT                             | OUT    |

| 39          | RCLK  | V24 (115) CIRCUIT                             | OUT    |

| 2           | TxD   | V24 (103) CIRCUIT (DATA TRANSMISSION)/X21 (T) | IN*    |

| 3           | RxD   | V24 (104) CIRCUIT (DATA RECEPTION)/X21 (R)    | OUT    |

| 4           | RTS   | V24 (105) CIRCUIT (REQUEST TO SEND)           | IN*    |

| 5           | CTS   | V24 (106) CIRCUIT (CLEAR TO SEND)             | OUT    |

| 6           | DSR   | V24 (107) CIRCUIT (DATA SET READY)/X21 (I)    | OUT    |

| 7           | DTR   | V24 (108) CIRCUIT (TERMINAL READY)/X21 (C)    | IN*    |

| 8           | DCD   | V24 (109) CIRCUIT (DATA CARRIER DETECT)       | OUT    |

| 9           | RING  | V24 (125) CIRCUIT (CALL INDICATE)             | OUT    |

| 10          | PDWN  | POWER DOWN                                    | IN*    |

| 24          | RESET | RESET INPUT                                   | IN*    |

| 21          | TRS   | TRANSMISSION START                            | OUT    |

| 1-12-23-34  | VSS   | GROUND                                        |        |

| 11-22-33-44 | VCC   | POSITIVE SUPPLY (+ 5 V)                       |        |

\* with internal pull-up resistor.

### **Functional Description**

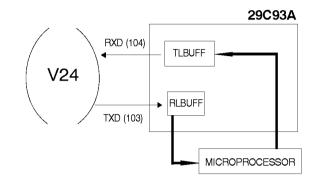

### **Asynchronous Mode**

### Data Format

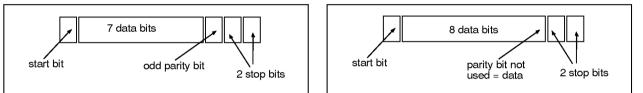

The TRAC can be programmed (in FASYNC register) to receive following data formats (parity included) :

5 bits with parity

5 bits without parity

6 bits with parity\*

7 bits with parity

7 bits without parity

8 bits without parity

8 bits with parity

9 bits with parity\*

The parity can be odd, even, forced low, forced high. The number of stop bits can be 1,1.5,2 (see table 2 in &5.1.1. of ECMA 102 rec.) except for (\*) which have a number of stop bits automatically fixed to 1 (if parity is used). Concerning the parity bit, and when the buffers are used (RLBUFF, RDBUFF, TLBUFF or TDBUFF), the TRAC behaves as follows :

<u>In reception</u>: the parity test (if parity is used, that means [P0, P1, P2] not equal to [0, 0, 0]) is reported in INT0 register (PARL bit on local side, PARD bit on distant side).

<u>In transmission</u>: The parity bit is calculated by the TRAC for all data formats. This parity bit can be forced right (by writing in TLBUFF or TDBUFF) or forced wrong (by writing in ERRTL or ERRTD). This feature is specially useful in flow control mode using 9 bit data format. For example, if data is received with an erroneous parity bit, it can be sent with the same erroneous parity bit using a single write in ERRTL (on local side) or in ERRTD (on distant side).

### Break Management

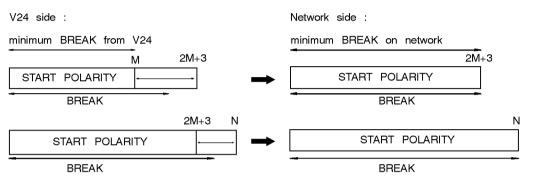

The TRAC will also handle BREAK signal as specified in ECMA 102/V110 recommendation. If the circuit detects M to 2M + 3 bits of start polarity where M is the number of bits per character in the selected format including start/stop bits, it will transmit 2M + 3 bits of start polarity. If the circuit detects more than 2M + 3 bits of start polarity, it will transmit all these bits of start polarity. The 2M + 3 or more bits of start polarity, received from the transmitting side of a remote terminal shall be output to the receiving local terminal. The TRAC must receive from terminal/modem at least 2M bits of stop polarity on circuit 103, before being able to send further data characters (terminal or modem resynchronization).

#### Speed Adaptation

The overspeed and underspeed control will be automatically performed by the TRAC (&5.2.2. of ECMA 102/V110 rec.). If frames with only one stop bit per character are assembled, only one stop bit every 8 character might be removed by transmit controller. When overspeed is detected, the receiver will re-insert the deleted stop bit.

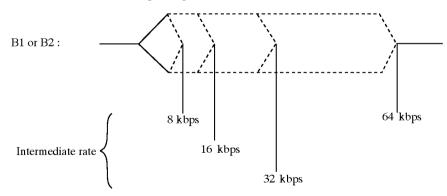

The TRAC circuit supports all ECMA 102/V110 specified asynchronous speeds (see table 1 below). Different speeds can be programmed in the receive and transmit path. Consequently terminals with different speeds can be connected. According to ECMA 102 specification, the 2 terminals must use the same intermediate rate.

| 19 | ble |   | • |

|----|-----|---|---|

| 1a | on  | 1 | ٠ |

| Data Rate | Rate Tolerance In % |

|-----------|---------------------|

| 50        | +/-2.5              |

| 75        | +/-2.5              |

| 110       | +/-2.5              |

| 150       | +/-2.5              |

| 200       | +/-2.5              |

| 300       | +/-2.5              |

| 600       | + 1 / -2.5          |

| 1200      | + 1 / -2.5          |

| 2400      | + 1 / -2.5          |

| 3600      | + 1 / -2.5          |

| 4800      | + 1 / -2.5          |

| 7200      | + 1 / -2.5          |

| 9600      | + 1 / -2.5          |

| 12000     | + 1 / -2.5          |

| 14400     | + 1 / -2.5          |

| 19200     | + 1 / -2.5          |

| 38400     | *                   |

| 57600     | *                   |

ECMA 102/V110 (except\*) specification for ASYNC speeds.

### Data Path

As stated earlier, local / end to end flow control and IPE re-entering modes can be implemented with the TRAC (and APPENDIX, register set : CONF and TFRM registers).

## **TEMIC** MATRA MHS

For V25bis protocol implementation the associated microprocessor is used. The TRAC connects its V24 interface to parallel  $\mu$ P port (UART feature). Once the call is established the UART block is connected back to

### Figure 1.

CONF register).

### Smart Modem

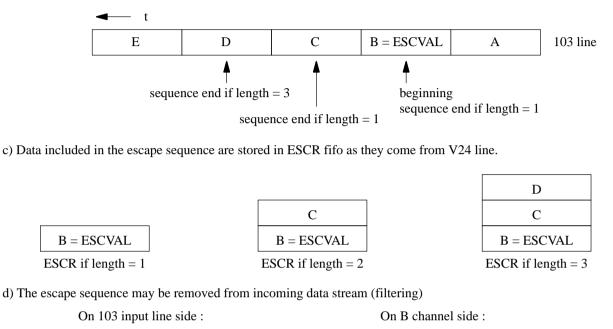

When working in transparent mode (no  $\mu$ P action, data are going straight from V24 (103) input to DOUT output), the 29C93A may be programmed to detect an escape character and report it to the  $\mu$ P (via an interrupt). To do this, the user should follow several steps summarized below :

- An escape sequence is 1, 2 or 3 word length. This length is stored in ESCMOD register.

- Only the first word of the sequence (loaded in ESCVAL register) will be compared with each of the incoming V24 data.

- The detection of this word in the stream is reported in ESCSTA register (BEG bit = beginning of sequence detected = 1) if it is enabled in ESCMOD register (EIBEG bit = 1).

- When the first character of the escape sequence is detected, the remaining data (until the sequence length is reached) are stored in a FIFO (at address 0F = ESCR). These data may be removed (filtered) from the data stream or sent toward the distant terminal depending on FSEQ bit in ESCMOD register.

- When the number of data received from the beginning of the sequence is equal to the sequence length, the END status bit in ESCSTA register is set to 1 if mask bit EIEND = 1 in ESCMOD.

- In one of the BEG or END bit is set, the ESC bit = global escape status bit will be set to 1 and will involve an active level on INT pin if unmasked (AIESC bit in MASK register = 1).

- Then the TRAC will automatically configure itself to "transmit flow control" mode (that is equivalent to

EPA = 1 in CONF register) if AUTO bit is set to 1 in ESCMOD register. In that case, the FC bit in ESCSTA will report the new configuration. EPA bit will remain unchanged.

RA0 for frame processing (APPENDIX, register set :

Local and remote loopback may also be programmed

(APPENDIX, register set : TFRM register)

- Then user can read the FIFO (via ESCR) in order to check if the received sequence is the expected one. Two pointers are available in the ESCSTA register :

- WPT which points at the last received character (particularly useful to determine which is the last character received when the end of the sequence is not detected after a given delay).

- RPT which points at the next character to read.

- Spurious sequence : if FSEQ = 1 (sequence remove from data stream), data may be lost if we do not pass automatically to flow control mode (we could not be able to insert this spurius sequence in the stream if characters follow).

### Synchronous Block

The TRAC handles all ECMA 102 speeds for synchronous transmissions (see table 2). For speeds up to 19200 bps, a 80 bit frame is used. Above 19200 bps we will have :

For 48 kbps, a special 32 bits frame. It will handle the X, SA/SB process on the X, S1, S3, S4 bits.

For 56 kbps, a 64 bit frame without inband signalling (8th bit forced high, see & 5.5 of ECMA 102).

For 64 kbps, the TRAC will be transparent (with no frame and no inband signalling). This speed will also be used for Inband Parameters Exchange (IPE).

### **Interface to ISDN Driver**

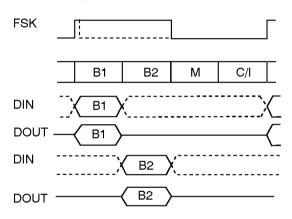

### B Channel

The TRAC can be programmed to interface with various synchronous serial buses (and so, with most of S0 interface circuits on the market). Some of them are described in APPENDIX (register set, CLKSEL register).

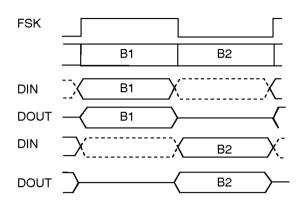

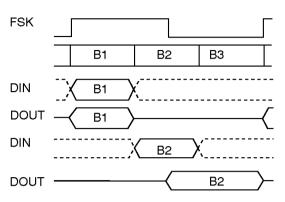

The TRAC can also be programmed to transmit data on B1 or B2 channel (B2 bit in TFRM register). DOUT output will be in high impedance state except during B1 or B2. It means there will be no status/command exchange between TRAC and other ISDN circuit(s).

Transmit window width programming is made according to intermediate speed (bit V3...0 in CLKSEL register). Outside that window, DOUT will be in high impedance allowing data multiplexing according to I460. Appropriate FSK sync. pulses must be provided for each TRAC connected on the same DOUT line.

| Table | 2 | : |

|-------|---|---|

|-------|---|---|

| Data Rate | Intermediate Rate      |

|-----------|------------------------|

| 600       | 8kbps                  |

| 1200      | 8kbps                  |

| 2400      | 8kbps                  |

| 4800      | 8kbps                  |

| 7200*     | 16kbps                 |

| 9600      | 16kbps                 |

| 12000*    | 32kbps                 |

| 14400*    | 32kbps                 |

| 19200     | 32kbps                 |

| 48000     | SINGLE STEP ADAPTATION |

| 56000     | SINGLE STEP ADAPTATION |

| 64000     | SINGLE STEP ADAPTATION |

\* As stated earlier the Network Independent Clock (NIC) mode will be supported by TRAC except for 7200/14400 bps.

### Network Independent Clock

For SYNC transmission using Network Independent Clock, phase difference between network and V24 clocks (R1 rate) must be measured (see &8 of ECMA 102), that is to say between :

a 20xR1 clock network synchronized generated from a 2048, 1536, 512 or 192 kHz clock connected to NREF input using a DPLL and a 12 or 7 MHz master clock. and a receive bit-timing sync. clock : V24 - 113 NETWORK INDEPENDENT TRANSMIT CLOCK (ITCLK).

### **Microprocessor Interface and Clocks**

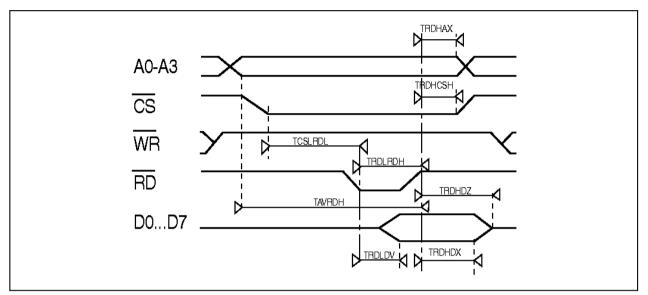

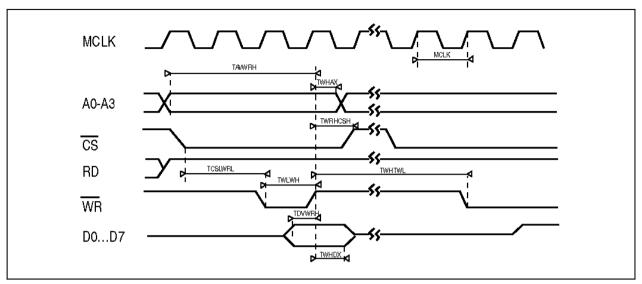

The TRAC has a 8 bit slave  $\mu P$  interface including :

- 8 bit parallel data port

- 4 bit address port for internal register selection

- 1 interrupt output, each interrupt source can be selectively masked (except loss of synchroni-zation interrupt).

- 1 Chip Select input

- RD/WR control inputs

The TRAC master clock MCLK (used by the UART baud generator) must be 12.288 MHz or 7.68 MHz (selected by an internal mode register). The TRAC also has a RESET input to clear internal registers and state machines.

### V24 Interchange Circuits

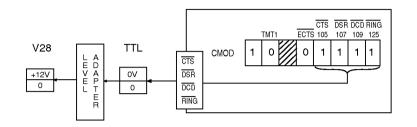

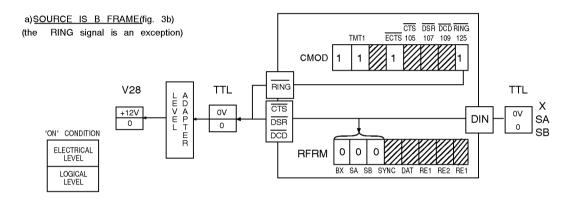

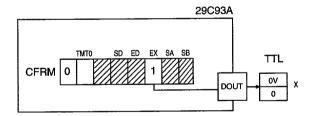

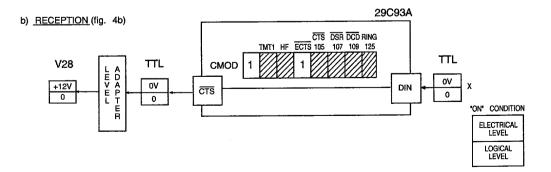

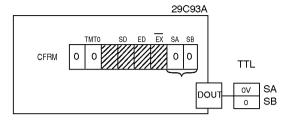

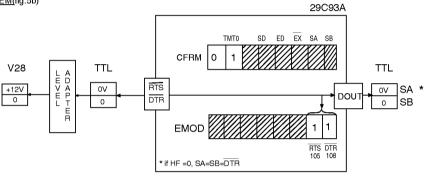

All output interchange circuits can be monitored using the μP interface (via CMOD register at 00 address, fig. 3a). They also can be driven by SA, SB, and × bits recovered from incoming frame (except RING fig. 3b.). For example, in the "END TO END" flow control situation, the 105 interchange line may be driven either by CTS bit in CMOD register or by × bit from incoming frame depending on ECTS bit (also in CMOD register, figures 3a, 3b, 4b).

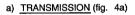

NOTE : X bit can only be driven by  $\overline{EX}$  bit in CFRM register (fig. 4a).

• Input interchange circuits 105 (RTS) and 108 (DTR) are continuously sampled and stored in EMOD (0a address) register. They can drive the associated SA, SB bits in outgoing frame (fig. 5a). In the opposite case, SA and SB can be driven independently in CFRM register (fig. 5b).

NOTE : Adaptation to X21 protocol controller (such as MHS 29C921) may be achieved using 108 ( $\overline{\text{DTR}}$ ) V24 input as C (Command) X21 circuit and 107 ( $\overline{\text{DSR}}$  V24 output as I (Indicate) X21 circuit.

### **Inband Parameter Exchange**

Because the R line does not provide the capability of OUT-OF-BAND signalling (like the D channel with the S line), the V110 (APPENDIX I, 1988) or ECMA123

# Τεμις

### MATRA MHS

recommendation define an INBAND PARAMETER EXCHANGE (IPE) protocol to support :

- the transfer of the END-TO-END information required for the compatibility checking of data calls,

- an exchange of terminal adaptor parameter information, and

- an exchange of information related to maintenance operations.

Four IPE user data/intermediate rates are also recommended :

#### Table 3 :

| Connection Type           | IPE User Rate   |

|---------------------------|-----------------|

| unrestricted 64 kb/s      | 64 kb/s sync    |

| restricted 64 kb/s        | 56 kb/s sync    |

| 32 kb/s intermediate rate | 19.2 kb/s async |

| 16 kb/s intermediate rate | 9.6 kb/s async  |

Recommended user data/intermediate rates

The 29C93A supports IPE for all these speeds (and even for all RA0 synchronous rates) but character filte-ring works only at 64 or 56 kb/s (with synchronous data).

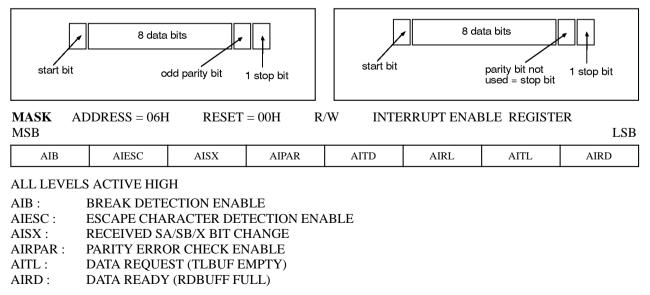

Synchronous IPE also requires transmission of at least 32 times for each command byte. This feature is avail-able in the TRAC. A repeated transmission is obtained by writing in IPEBUFF register. TDI status bit will appear in INTO register after each transmission, but no interrupt is generated on INT pin, even if it is unmasked (AITD = 1 in MASK register. To stop the repetition (for example to send high-low IPE data bytes) we just have to write a byte in TDBUFF, which will be shifted only once. Then the transmitter sends "1" (INACTIVE character), and TDI bit is set until a new datum or command is written in TDBUFF or IPEBUFF.

### **Summary**

a) synchronous IPE (synchronous primary mode)

- on DIN/DOUT : bytes aligned with FSK network clock (no start bit, no frame),

- user data rate : 56 or 64 KBPS

for restricted 64 kb/s rate, the MSB of the byte must be set to 1.

29C93A

- byte filtering in reception. (see table 4)

- byte transmission with auto-repeat capability (using IPEBUFF register).

b) asynchronous IPE (asynchronous primary mode)

- on DIN/DOUT : rate adaptation (V110/ ECMA102) ==> FRAME,

- asynchronous format (START + STOP),

- user data rate : 600 to 19200 kb/s.

### **Byte Filtering**

#### Table 4 :

|        | Value (H) | Message     |

|--------|-----------|-------------|

|        | E0        | PARAM-0     |

|        | E2        | PARAM-4     |

| C<br>O | E4        | PARAM-2     |

| М      | E6        | X_START     |

| M<br>A | E8        | PARAM-1     |

| N<br>D | EA        | RA-VERSION  |

|        | EC        | PARAM-3     |

|        | EE        | MAINTENANCE |

| S      | FA        | READY       |

| T<br>A | FB        | FILL        |

| T<br>U | FE        | IDLE        |

| S      | FF        | INACTIVE    |

### **Power Down**

Driving pin PDWN low activates the power down mode. Once in power down, most of the signals (see table 5) are disconnected to reduce power consumption. The TRAC is thus isolated from its environment (this feature is useful for board testing).

### V24 SIGNALS (from 29C93A)

a)SOURCE IS CMOD REGISTER (fig. 3a)

**BIT MANAGEMENT**

#### a)SOURCE IS CFRM REGISTER (fig. 5a)

### V24 SIGNALS SA/SB GENERATION

a)S<u>OURCE\_IS\_MODEM(</u>fig.5b)

### Table 5 : Power Down Mode.

| Pin   | Input        | Output      |

|-------|--------------|-------------|

| D0:D7 | DISCONNECTED | HI-Z        |

| A0:A3 | DISCONNECTED | -           |

| CS    | DISCONNECTED | -           |

| RD    | DISCONNECTED | -           |

| WR    | DISCONNECTED | -           |

| INT   | -            | FORCED HIGH |

| BCLK  | DISCONNECTED | -           |

| MCLK  | DISCONNECTED | -           |

| NREF  | DISCONNECTED | -           |

| DIN   | DISCONNECTED | -           |

| DOUT  | -            | HI-Z        |

| FSK   | DISCONNECTED | -           |

| ITCLK | DISCONNECTED | -           |

| TCLK  | -            | FORCED HIGH |

| RCLK  | -            | FORCED HIGH |

| TXD   | -            | -           |

| RXD   | -            | FORCED HIGH |

| RTS   | -            | -           |

| CTS   | -            | FORCED HIGH |

| DSR   | -            | FORCED HIGH |

| DTR   |              | -           |

| DCD   | -            | FORCED HIGH |

| RING  | -            | FORCED HIGH |

| RESET | -            | -           |

## TEMIC MATRA MHS

## Appendix – Register Set

| CMOD       00H       81H       1       TMT1       HF       ECTS       DTS       DCD       RING       RW         CFRM       00H       00H       0       TMT0       -       SD       ED       EX       SA       SB       RW         CONF       01H       00H       AT       AS       EPA       SPA       LOCAL APRIM       TINC       RNIC       RW         TFRM       02H       00H       -       RFILT       SPRIM       TBL       BL       TBD       VD       B2       RW         CLKSEL       03H       00H       BTYPI       BTYP0       REF1       REF0       V3       V2       V1       V0       RW         ASCLK       04H       20/40H       -       TRSEL       RRSEL       AR4       AR3       AR2       AR1       AR0       RW         ASCLK       04H       20/40H       -       TRSEL       RRSEL       AR4       AR3       AR2       AR1       AR0       RW         ASCLK       04H       20/40H       -       TRSEL       RRSEL       AR4       AR3       AR2       AR1       AR0       RW         ASS       06H       00H <td< th=""><th>NAME</th><th>ADD</th><th>RESET</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th>RD/WR</th></td<> | NAME    | ADD | RESET  |       |                                        |         |         |         |         |        |       | RD/WR          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|--------|-------|----------------------------------------|---------|---------|---------|---------|--------|-------|----------------|

| CONF01H00HATASEPASPALOCALAPRIMTINCRNICRWTFRM02H00H-RFILTSPRIMTBLBLTBDVDB2RWCLKSEL03H00HBTYP1BTYP0REF1REF0V3V2V1V0RWASCLK04H20/40H-TRSELRRSELAR4AR3AR2AR1AR0RWFASYNC05H00HH0NS1NS0ND1ND0P2P1P0RWMASK06H00HAIBAIESCAISXAIPARAITDAIRLAITLAIRDRWRLBUFF07H0CHLOCAL RECEIVE BUFFERRRTLBUFF08H00HDISTANT RECEIVE BUFFERWRFRM09HEFHEXSASBSYNCDATRE3RE2RE1RERRTD09H-TRANSMISSION TO DISTANT TRANSMIT BUFFERWWWWWWWINTO0BH00HISELPARLRLITLIPARDDSXRDITDIRIPE COMMAND TRANSMIT BUFFERWISELESCBRKLEBKDWWINT10CH00HISELESCBRKLOSYNCBRKDOVRSRERKT0CHBRKLEBKDWWISELESCRWIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CMOD    | 00H | 81H    | 1     | TMT1                                   | HF      | ECTS    | CTS     | DSR     | DCD    | RING  | R/W            |

| TFRM02H00H-RFILTSPRIMTBLBLTBDVDB2RWCLKSEL03H00HBTYP1BTYP0REF1REF0V3V2V1V0RWASCLK04H20/40H-TRSELRRSELAR4AR3AR2AR1AR0RWASCLK04H20/40H-TRSELRRSELAR4AR3AR2AR1AR0RWASCLK04H20/40H-TRSELRRSELAR4AR3AR2AR1AR0RWFASYNC05H00HH0NS1NS0ND1ND0P2P1P0RWMASK06H00HAIBAIESCAISXAIPARAITDAIRLAITLAIRDRWRLBUFF07H0CHLOCALRECEIVE BUFFERRWRDBUFF08H00HDISTANT RECEIVE BUFFERWRFRM09HEFHBXSASBSYNCDATRE3RE2RE1RERRTD09H-TRANSMISSION TO DISTANT WITH WRONG PARITYWEMCD0AH*RTSDTRRINT00BH00HISELPARLRLITLIPARDDSXRDITDIRIPEBUFF0BH-IPECOMMAND TRANSMIT BUFFERWWINT1OCHOHISELESCBRKLOVR24-DSYNCBRKD<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CFRM    | 00H | 00H    | 0     | тмто                                   | -       | SD      | ED      | EX      | SA     | SB    | R/W            |

| CLKSEL       03H       00H       BTYP1       BTYP1       BTYP0       REF1       REF0       V3       V2       V1       V0       RW         ASCLK       04H       20/40H       -       TRSEL       AR4       AR3       AR2       AR1       AR0       RW         FASYNC       05H       00H       H0       NS1       NS0       ND1       ND0       P2       P1       P0       RW         MASK       06H       00H       AIB       AIESC       AISX       AIPAR       AITD       AIRL       AITL       AIRD       RW         RLBUFF       07H       0CH       LOCAL RECEIVE BUFFER       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R                                                                                                                                                          | CONF    | 01H | 00H    | AT    | AS                                     | EPA     | SPA     | LOCAL   | APRIM   | TINC   | RNIC  | R/W            |

| ASCLK       04H       20/40H       -       TRSEL       AR4       AR3       AR2       AR1       AR0       R/W         FASYNC       05H       00H       H0       NS1       NS0       ND1       ND0       P2       P1       P0       R/W         MASK       06H       00H       AIB       AIESC       AISX       AIPAR       AITD       AIRL       AITL       AIRD       R/W         MASK       06H       00H       AIB       AIESC       AISX       AIPAR       AITD       AIRL       AITL       AIRD       R/W         RLBUFF       07H       0CH       LOCAL TRANSMIT BUFFER       R       R       W       R       R       R       W       R       R       R       W       R       R       R       R       R       R       W       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R                                                                                                                                                    | TFRM    | 02H | 00H    | -     | RFILT                                  | SPRIM   | TBL     | BL      | TBD     | VD     | B2    | R/W            |

| FASYNC05H00HH0NS1NS0ND1ND0P2P1P0RWMASK06H00HAIBAIESCAISXAIPARAITDAIRLAITLAIRDRWRLBUFF07H0CHLOCAL RECEIVE BUFFERRTLBUFF07H00HLOCAL TRANSMIT BUFFERWRDBUFF08H00HDISTANT RECEIVE BUFFERRTDBUFF08H00HDISTANT TRANSMIT BUFFERWRFRM09HEFHBXSASBSYNCDATRE3RE2RE1RERRTD09H-TRANSMISSION TO DISTANT WITH WRONG PARITYWEMCD0AH*RTRANSMISSION TO LOCAL WITH WRONG PARITYWINT00BH00HISELPARLRLITLIPARDDSXRDITDIRINT10CH00HISELESCBRKLOVR24DSYNCBRKDOVRSRERKT0CHBRKLEBKDWINT10CH00HISELESCBRKLOVR24DSYNCBRKDOVRSRERKT0CH0FSEQAUTOEIENDEIBEGENESCLONGIRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CLKSEL  | 03H | 00H    | BTYP1 | BTYP0                                  | REF1    | REF0    | VЗ      | V2      | V1     | VO    | R/W            |

| MASK06H00HAIBAIESCAISXAIPARAITDAIRLAITLAIRDR/WRLBUFF07H0CHLOCAL RECEIVE BUFFERRTLBUFF07H00HLOCAL TRANSMIT BUFFERWRDBUFF08H00HDISTANT RECEIVE BUFFERRTDBUFF08H00HDISTANT RECEIVE BUFFERWRFRM09HEFHBXSASBSYNCDATRE3RE2RE1RERRTD09H-TRANSMISSION TO DISTANT WITH WRONG PARITYWEMCD0AH*RTSDTRRINTO0BH00HISELPARLRLITLIPARDDSXRDITDIRINT10CH00HISELESCBRKLOVR24-DSYNCBRKDOVRSRERKT0CHBRKLEBKD-WINT10CH00HISELESCBRKLOVR24-DSYNCBRKDOVRSRERKT0CHBRKLEBKDWWESCMOD0DH00H0FSEQAUTOEIENDEIBEGENESCLONG0RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ASCLK   | 04H | 20/40H | -     | TRSEL                                  | RRSEL   | AR4     | AR3     | AR2     | AR1    | AR0   | R/W            |

| RLBUFF       07H       0CH       LOCAL RECEIVE BUFFER       R         TLBUFF       07H       00H       LOCAL TRANSMIT BUFFER       W         RDBUFF       08H       00H       DISTANT RECEIVE BUFFER       R         TDBUFF       08H       00H       DISTANT RECEIVE BUFFER       R         RFRM       09H       EFH       BX       SA       SB       SYNC       DAT       RE3       RE2       RE1       R         ERRTD       09H       -       TRANSMISSION TO DISTANT WITH WRONG PARITY       W         ERRTL       0AH       -       TRANSMISSION TO LOCAL WITH WRONG PARITY       W         INT0       0BH       00H       ISEL       PARL       RLI       TLI       PARD       DSX       RDI       TDI       R         IPEBUFF       0BH       -       IPE COMMAND TRANSMIT BUFFER       W       W         INT1       0CH       00H       ISEL       ESC       BRKL       OVR24       DSYNC       BRKD       OVRS       R         ERKT       0CH       -       -       BRKL       -       -       EBKD       W         INT1       0CH       0H       ISEL       ESC       BRKL       -<                                                                                          | FASYNC  | 05H | 00H    | Но    | NS1                                    | NS0     | ND1     | ND0     | P2      | P1     | P0    | R/W            |

| TLBUFF       07H       00H       LOCAL TRANSMIT BUFFER       W         RDBUFF       08H       00H       DISTANT RECEIVE BUFFER       R         TDBUFF       08H       00H       DISTANT TRANSMIT BUFFER       W         RFRM       09H       EFH       BX       SA       SB       SYNC       DAT       RE3       RE2       RE1       R         ERRTD       09H       -       TRANSMISSION TO DISTANT WITH WRONG PARITY       W         EMCD       0AH       *       -       -       -       RTS       DTR       R         ERRTL       0AH       -       TRANSMISSION TO LOCAL WITH WRONG PARITY       W         INTO       0BH       00H       ISEL       PARL       RLI       TLI       PARD       DSX       RDI       TDI       R         IPEBUFF       0BH       -       IPE COMMAND TRANSMIT BUFFER       W       W       INT1       OCH       00H       ISEL       ESC       BRKL       OVR24       DSYNC       BKD       OVRS       R         ERKT       0CH       -       -       BRKL       -       -       EBKD       W         INT1       0CH       00H       ISEL       ESC                                                                                                  | MASK    | 06H | 00H    | AIB   | AIESC                                  | AISX    | AIPAR   | AITD    | AIRL    | AITL   | AIRD  | R/W            |

| RDBUFF       08H       00H       DISTANT RECEIVE BUFFER       R         TDBUFF       08H       00H       DISTANT RECEIVE BUFFER       R         TDBUFF       08H       00H       DISTANT TRANSMIT BUFFER       W         RFRM       09H       EFH       BX       SA       SB       SYNC       DAT       RE3       RE2       RE1       R         ERRTD       09H       -       TRANSMISSION TO DISTANT WITH WRONG PARITY       W         EMCD       0AH       *       -       -       -       RTS       DTR       R         ERRTL       0AH       -       TRANSMISSION TO LOCAL WITH WRONG PARITY       W         INT0       0BH       00H       ISEL       PARL       RLI       TLI       PARD       DSX       RDI       TDI       R         IPEBUFF       0BH       -       IPE COMMAND TRANSMIT BUFFER       W       W       INT1       OCH       OH       ISEL       ESC       BRKL       OVR24       DSYNC       BRKD       OVRS       R         ERKT       OCH       -       -       BRKL       -       -       EBKD       W         INT1       OCH       0       FSEQ       AUTO                                                                                                  | RLBUFF  | 07H | 0CH    |       | LOCAL RECEIVE BUFFER                   |         |         |         |         |        |       | R              |

| TDBUFF       08H       00H       DISTANT TRANSMIT BUFFER       W         RFRM       09H       EFH       BX       SA       SB       SYNC       DAT       RE3       RE2       RE1       R         ERRTD       09H       -       TRANSMISSION TO DISTANT WITH WRONG PARITY       W         EMCD       0AH       *       -       -       -       RTS       DTR       R         ERRTL       0AH       -       TRANSMISSION TO LOCAL WITH WRONG PARITY       W         INT0       0BH       00H       ISEL       PARL       RLI       TLI       PARD       DSX       RDI       TDI       R         IPEBUFF       0BH       -       IPE COMMAND TRANSMIT BUFFER       W       W       INT1       0CH       00H       ISEL       ESC       BRKL       OVR24       DSYNC       BRKD       OVRS       R         ERKT       0CH       -       -       BRKL       -       -       EBKD       W         INT1       0CH       00H       0       FSEQ       AUTO       EIBEG       ENSC       LONG1       RW                                                                                                                                                                                           | TLBUFF  | 07H | 00H    |       | LOCAL TRANSMIT BUFFER                  |         |         |         |         |        |       | w              |

| RFRM       09H       EFH       BX       SA       SB       SYNC       DAT       RE3       RE2       RE1       R         ERRTD       09H       -       TRANSMISSION TO DISTANT WITH WRONG PARITY       W         EMCD       0AH       *       -       -       -       RTS       DTR       R         ERRTL       0AH       *       -       -       -       -       RTS       DTR       R         ERRTL       0AH       -       TRANSMISSION TO LOCAL WITH WRONG PARITY       W         INTO       0BH       00H       ISEL       PARL       RLI       TLI       PARD       DSX       RDI       TDI       R         IPEBUFF       0BH       -       IPE COMMAND TRANSMIT BUFFER       W       W         INT1       0CH       00H       ISEL       ESC       BRKL       OVR24       DSYNC       BRKD       OVRS       R         ERKT       0CH       -       -       BRKL       -       -       EBKD       W         ESCMOD       0DH       00H       0       FSEQ       AUTO       EIBEG       ENESC       LONG1       RW                                                                                                                                                                   | RDBUFF  | 08H | 00H    |       | DISTANT RECEIVE BUFFER                 |         |         |         |         |        |       | R              |

| ERRTD       09H       -       TRANSMISSION TO DISTANT WITH WRONG PARITY       W         EMCD       0AH       *       -       -       -       R         ERRTL       0AH       *       -       -       -       R         ERRTL       0AH       *       TRANSMISSION TO LOCAL WITH WRONG PARITY       W         INTO       0BH       00H       ISEL       PARL       RLI       TLI       PARD       DSX       RDI       TDI       R         INTO       0BH       00H       ISEL       PARL       RLI       TLI       PARD       DSX       RDI       TDI       R         INT1       0CH       00H       ISEL       ESC       BRKL       OVR24       OSYNC       BRKD       OVRS       R         ERKT       0CH       -       -       BRKL       -       -       EBKD       W         ESCMOD       0DH       00H       0       FSEQ       AUTO       EIEND       EIBEG       ENESC       LONG1       R/W                                                                                                                                                                                                                                                                                     | TDBUFF  | 08H | 00H    |       | DISTANT TRANSMIT BUFFER                |         |         |         |         |        |       | $\overline{w}$ |

| EMCD       0AH       *       -       -       -       -       RTS       DTR       R         ERRTL       0AH       -       TRANSMISSION TO LOCAL WITH WRONG PARITY       W         INTO       0BH       00H       ISEL       PARL       RLI       TLI       PARD       DSX       RDI       TDI       R         IPEBUFF       0BH       -       IPE COMMAND TRANSMIT BUFFER       W         INT1       0CH       00H       ISEL       ESC       BRKL       OVR24       -       DSYNC       BRKD       OVRS       R         ERKT       0CH       -       -       BRKL       -       -       EBKD       W         ESCMOD       0DH       00H       0       FSEQ       AUTO       EIBEG       ENESC       LONG1       LONG0                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RFRM    | 09H | EFH    | BX    | SA                                     | SB      | SYNC    | DAT     | RE3     | RE2    | RE1   | R              |

| ERRTL       0AH       -       TRANSMISSION TO LOCAL WITH WRONG PARITY       W         INTO       0BH       00H       ISEL       PARL       RLI       TLI       PARD       DSX       RDI       TDI       R         IPEBUFF       0BH       -       IPE COMMAND TRANSMIT BUFFER       W         INT1       0CH       00H       ISEL       ESC       BRKL       OVR24       -       DSYNC       BRKD       OVRS       R         ERKT       0CH       -       -       BRKL       -       -       EBKD       -       W         ESCMOD       0DH       00H       0       FSEQ       AUTO       EIBEG       ENESC       LONG1       R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ERRTD   | 09H | -      | TRA   | ANSMIS                                 | SION TO | O DISTA | NT WIT  | H WRO   | NG PAF | NTY   | w              |

| INTO       0BH       00H       ISEL       PARL       RLI       TLI       PARD       DSX       RDI       TDI       R         IPEBUFF       0BH       -       IPE COMMAND TRANSMIT BUFFER       W         INT1       0CH       00H       ISEL       ESC       BRKL       OVR24       -       DSYNC       BRKD       OVRS       R         ERKT       0CH       -       -       BRKL       -       -       EBKD       -       W         ESCMOD       0DH       00H       0       FSEQ       AUTO       EIBEG       ENESC       LONG1       LONG0       R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EMCD    | 0AH | *      | -     | -                                      | -       | -       | -       | -       | RTS    | DTR   | R              |

| IPEBUFF       0BH       -       IPE COMMAND TRANSMIT BUFFER       W         INT1       0CH       00H       ISEL       ESC       BRKL       OVR24       -       DSYNC       BRKD       OVRS       R         ERKT       0CH       -       -       BRKL       -       -       EBKD       -       W         ESCMOD       0DH       00H       0       FSEQ       AUTO       EIEND       EIBEG       ENESC       LONG1       LONG0       R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ERRTL   | 0AH | -      | TF    | RANSMI                                 | SSION   | TO LOC  | AL WITI | H WRON  | NG PAR | ITY   | $\overline{w}$ |

| INT1 OCH OOH ISEL ESC BRKL OVR24 - DSYNC BRKD OVRS R<br>ERKT OCH BRKL EBKD - W<br>ESCMOD ODH OOH O FSEQ AUTO EIEND EIBEG ENESC LONG1 LONGO R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | INTO    | овн | 00H    | ISEL  | PARL                                   | RLI     | TLI     | PARD    | DSX     | RDI    | TDI   | R              |

| ERKT       0CH       -       -       BRKL       -       -       EBKD       -       W         ESCMOD       0DH       00H       6       FSEQ       AUTO       EIEND       EIBEG       ENESC       LONG1       LONG0       R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IPEBUFF | овн | -      |       | IPE COMMAND TRANSMIT BUFFER            |         |         |         |         |        |       | w              |

| ESCMOD 0DH 00H 0 FSEQ AUTO EIEND EIBEG ENESC LONG1 LONG0 R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | INT1    | 0CH | 00H    | ISEL  | ESC                                    | BRKL    | OVR24   | -       | DSYNC   | BRKD   | OVRS  | R              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ERKT    | 0CH | -      | _     | -                                      | BRKL    | -       | -       | -       | EBKD   | -     | $\overline{W}$ |

| ESCSTA 0EH 00H ENESC FC RPT1 RPT0 WPT1 WPT0 END BEG R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ESCMOD  | ODH | 00H    | 0     | FSEQ                                   | AUTO    | EIEND   | EIBEG   | ENESC   | LONG1  | LONGC | R/₩            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ESCSTA  | 0EH | 00H    | ENESC | FC                                     | RPT1    | RPT0    | WPT1    | WPT0    | END    | BEG   | R              |

| ESCR 0FH 0CH ESCAPE SEQUENCE RECEIVED (3 BYTES MAX) R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ESCR    | 0FH | 0CH    |       | ESCAPE SEQUENCE RECEIVED (3 BYTES MAX) |         |         |         |         |        | R     |                |

| ESCVAL 0FH 00H PROGRAMMABLE ESCAPE VALUE W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ESCVAL  | 0FH | 00H    |       | F                                      | PROGR   | AMMABI  | LE ESC  | APE VAI | LUE    |       | $\overline{w}$ |

\* depends on circuit input states

# TEMIC

MATRA MHS

| CMOD A<br>MSB             | ADDRESS = 00H                                                                   | RESET = 8                                                                          | 31H R/W                                                              | MODEM SIG                         | NAL CONT         | ROL REGISTE                      | ER<br>LSB |

|---------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------|------------------|----------------------------------|-----------|

| 1                         | TMT1                                                                            | HF                                                                                 | ECTS                                                                 | CTS                               | DSR              | DCD                              | RING      |

|                           |                                                                                 |                                                                                    | •                                                                    | 106                               | 107              | 109                              | 125       |

| TMT1 :                    | DSR/DCD MO                                                                      | DEM SIGNA                                                                          | LS SOURCE                                                            | SELECT.                           |                  |                                  |           |

|                           | TMT1 =                                                                          |                                                                                    | CMOD regis<br>$n = not \overline{DSR} b$<br>$n = not \overline{DCD}$ | oit,                              |                  |                                  |           |

|                           | TMT1 =                                                                          | = 1 – Source is<br>DSR pir<br>DCD pir                                              | n = SA = SB i<br>= SA if HF =                                        | f HF = 0,                         |                  |                                  |           |

| HF :                      |                                                                                 | – FUL <u>L DU</u> PI                                                               | LEX / X21<br>pin = SA = S<br>LEX<br>n = SA,                          |                                   |                  |                                  |           |

| ECTS :                    |                                                                                 | $0 - \overline{\text{CTS}}$ pin =                                                  |                                                                      | n incoming fram                   | ne.              |                                  |           |

| $\overline{\text{CTS}}$ : | COMPLEMEN                                                                       | TARY VALU                                                                          | E OF CTS (C                                                          | LEAR TO SEN                       | D-106) PIN W     | HEN $\overline{\text{ECTS}} = 0$ | )         |

| DSR :                     |                                                                                 | TARY VALU<br>= 0 – DSR pin                                                         |                                                                      | DATA SET REA<br>t.                | DY-107) PIN V    | WHEN TMT1 =                      | = 0       |

| DCD : COM                 | IPLEMENTARY<br>WHEN TMT1                                                        | VALUE OF $\overline{\Gamma}$                                                       | DCD (DATA C                                                          | CARRIER DET                       | ECT-109) PIN     |                                  |           |

| RING :                    |                                                                                 | TARY VALU<br>in = not RING                                                         |                                                                      | CALLING IND                       | DICATOR-125)     | PIN                              |           |

| CMOD regine For 2 success | AD OPERATION<br>ster is read at addr<br>ssive read operati<br>MOD register will | ess 0 if the MS<br>ons at address                                                  | 0, we always                                                         | will recover 2                    | different values | s of this MSB,                   |           |

|                           | READ operation<br>MSB recovered<br>REGISTER com                                 | 1 :                                                                                | n<br>1<br>CMOD                                                       | n+ 1<br>0<br>CFRM                 | n+2<br>1<br>CMOD |                                  |           |

| CFRM A<br>MSB             | ADDRESS = 00H                                                                   | $\mathbf{RESET} = 0$                                                               | 0H W F                                                               | RAME SIGNA                        | L CONTRO         | L REGISTER                       | LSB       |

| 0                         | TMT0                                                                            |                                                                                    | SD                                                                   | ED                                | EX               | SA                               | SB        |

| TMT0 :                    |                                                                                 | = 0 – Source is<br>SA (bit fram<br>SB (bit fram<br>= 1 – Source is<br>SA (bit fram | CFRM regist<br>e) = SA (bit r<br>e) = SB (bit r                      | egister)<br>egister)<br>if HF = 0 |                  |                                  |           |

$=\overline{\text{RTS}}$  pin if HF = 1

| SD :                       | DATA BIT SELECT<br>SD = 0 - D = ED (for example $ED = 0$ during resync mode)<br>SD = 1 - D = TxD (103)                                                                                                                                |                                                                                                                                                                       |            |            |                |            |      |  |  |  |  |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|----------------|------------|------|--|--|--|--|

| ED :                       | DATA BIT TO                                                                                                                                                                                                                           | BE TRANSM                                                                                                                                                             | ITTED WHEN | N SD = 0   |                |            |      |  |  |  |  |

| $\overline{\mathrm{EX}}$ : | COMPLEMEN                                                                                                                                                                                                                             | COMPLEMENTARY VALUE OF X BIT TO BE TRANSMITTED                                                                                                                        |            |            |                |            |      |  |  |  |  |

| SA:                        | VALUE OF SA                                                                                                                                                                                                                           | VALUE OF SA BIT TO BE TRANSMITTED WHEN $TMT0 = 0$                                                                                                                     |            |            |                |            |      |  |  |  |  |

| SB:                        | VALUE OF SE                                                                                                                                                                                                                           | BIT TO BE 1                                                                                                                                                           | RANSMITTE  | ED WHEN TM | $\Gamma 0 = 0$ |            |      |  |  |  |  |

| NOTE : RE                  | AD OPERATION                                                                                                                                                                                                                          | I (SEE CMOD                                                                                                                                                           | REGISTER)  |            |                |            |      |  |  |  |  |

| CONF<br>MSB                | ADDRESS = 0                                                                                                                                                                                                                           | 1H RESE                                                                                                                                                               | ET = 00H   | R/W CO     | NFIGURATIO     | N REGISTER | LSB  |  |  |  |  |

| AT                         | AS                                                                                                                                                                                                                                    | EPA                                                                                                                                                                   | SPA        | LOCAL      | APRIM          | TNIC       | RNIC |  |  |  |  |

| AT :                       | Frame transmit $AT = 0$ -                                                                                                                                                                                                             | FRAME ENABLE<br>Frame transmit and synchronization enable after communication has been established.<br>AT = 0 – DOUT pin high impedance,<br>AT = 1 – transmit enable. |            |            |                |            |      |  |  |  |  |

| AS :                       | ASYNC / SYNC SELECT<br>AS = 0 – Synchronous,<br>AS = 1 – Asynchronous.                                                                                                                                                                |                                                                                                                                                                       |            |            |                |            |      |  |  |  |  |

| EPA :                      | <ul> <li>TRANSMIT FLOW CONTROL</li> <li>TDBUFF/RLBUFF register access through μP bus allowing local flow control between TRAC and near end terminal.</li> <li>EPA = 0 – access locked,</li> <li>EPA = 1 – access enabled :</li> </ul> |                                                                                                                                                                       |            |            |                |            |      |  |  |  |  |

|                            |                                                                                                                                                                                                                                       |                                                                                                                                                                       | 2909       | 3A         | В              |            |      |  |  |  |  |

### SPA : RECEIVE FLOW CONTROL

TLBUFF/RDBUFF register access through  $\mu P$  bus allowing distant flow control operation between TRAC and far-end terminal.

SPA=0 – access locked,

SPA=1 – parallel input/output enabled :

### MATRA MHS

LOCAL : LOCAL MODE ENABLE (for V25bis)

TLBUFF/RLBUFF registers access through  $\mu$ P bus allowing exchange with local terminal. LOCAL = 0 – access locked,

LOCAL = 1 - parallel input/output enabled.

APRIM = 1 - access enabled :

TNIC : ALLOWS E4, E5, E6 GENERATION IN TRANSMIT FRAME (except for 7.2/12/14.4 kbps, comparison between ITCLK (113) and ISDN network clocks).

TNIC = 0 - no compensation,

TNIC = 1 - compensation enabled - E bit generation.

RNIC : E4, E5, E6 bit decoding – TCLK/RCLK clock compensation. RNIC = 0 - no compensation, RNIC = 1 - compensation enabled – E bit decoding.

| <b>FFRM</b><br>MSB | ADDRESS = 0 | 2H RESE | ET = 00H | R/W TR | ANSMIT FRA | ME REGISTE | R<br>LSB |

|--------------------|-------------|---------|----------|--------|------------|------------|----------|

| •                  | RFILT       | SPRIM   | TBL      | BL     | TBD        | BD         | B2       |

### RFILT : FILTERING FOR INCOMING DATA

#### SPRIM : SYNCHRONOUS PRIMARY ACCESS (FOR INBAND PARAMETER EXCHANGE – 56/64 kbps) Enables parameter exchange after communication is established and before so

Enables parameter exchange after communication is established and before synchronization

### RFILT SPRIM

| 111 1121 | DI IUIII |                                                                           |

|----------|----------|---------------------------------------------------------------------------|

| 0        | 0        | no primary access                                                         |

| 0        | 1        | access to 64 (or 56) kbps synchronous primary mode                        |

| 1        | 0        | reserved                                                                  |

| 1        | 1        | access to 64 (or 56) kbps synchronous primary mode with IPE facilities    |

|          |          | (command byta, transmission with auto repeat via IDERUFE and command byta |

(command byte transmission with auto repeat via IPEBUFF and command byte filtering in reception)

# Τεміс

### MATRA MHS

TBL :DATA OUTPUT ENABLE (with LOCAL LOOPBACK mode only)TBL = 0 - data not enabled on B output (forced to 1)TBL = 1 - data enabled on B output during local loopback

BL : LOCAL LOOPBACK B transmitter output connected to B receiver input

- BL = 0 no loopback

- BL = 1 loopback enabled

\* Enabled by TBL bit

TBD : DATA OUTPUT ENABLE (with DISTANT LOOPBACK mode only) TBD = 0 - data not enabled on 104 output (forced to 1) TBD = 1 - data enabled on 104 output during distant loopback

#### BD : DISTANT LOOPBACK

TxD (103) connected to RxD (104) BD = 0 - no loopback

BD = 1 - loopback enabled

\* Enabled by TBD bit

B2 : B1/B2 CHANNEL SELECT B2 = 1 - B2 select B2 = 0 - B1 select

# ΤΕΜΙΟ

MATRA MHS

| CLKSEI<br>MSB | L A         | ADDRESS = 03H |              | RESET = 00H |     | R/W CLOC |    | K SELE | CTION R | EGISTER   | LSB |

|---------------|-------------|---------------|--------------|-------------|-----|----------|----|--------|---------|-----------|-----|

| BTYP          | BTYP1 BTYP0 |               | REF          | REF1        |     | V3       | V2 |        | V1      | V0        |     |

|               |             |               |              |             |     |          |    |        |         | •         |     |

| BTYP1         | BTYP0       | IN            | OUT          | BCLK        | PPG | REF1     |    | R      | EF0     | NREF (kHz | ()  |

| 0             | 0           | $\uparrow$    | $\downarrow$ | 1           | no  | 0        |    |        | 0       | 2048      |     |

| 0             | 1           | $\downarrow$  | Ŷ            | 1           | no  | 0        |    |        | 1       | 1536      |     |

| 1             | 0           | $\downarrow$  | Ŷ            | 1/2         | no  | 1        |    |        | 0       | 512       |     |

| 1             | 1           | $\downarrow$  | $\uparrow$   | 1           | YES | 1        |    |        | 1       | 192       |     |

IN = input sampling edge OUT = output driving edge

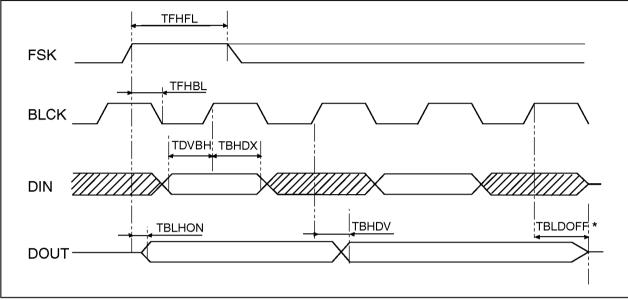

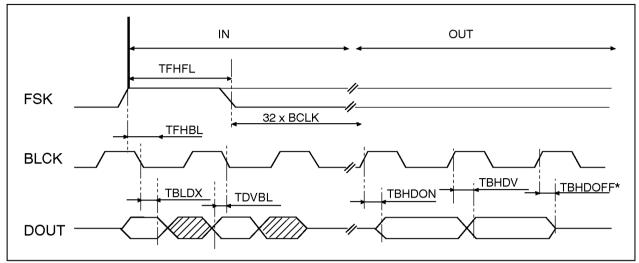

PPG = no – input/output on B channel side are simultaneous and synchronized with FSK frame sync clock.

PPG = yes – master/slave mode, input/output operations occur alternatively within 1/8 kHz period.

DOUT is used as I/O pin.

### EXAMPLES :

| BTYP<br>1 | BTYP<br>0 | BCLK<br>(kHz)* | FSK |       |    |   |     |       |    |   |     |  |

|-----------|-----------|----------------|-----|-------|----|---|-----|-------|----|---|-----|--|

| 0         | 0         | 192            |     | B1    |    |   |     | B2    |    | В |     |  |

| 0         | 1         | 128            |     | B1    |    |   |     | B2    |    |   |     |  |

| 1         | 0         | 512            |     | B1 B2 |    |   | 2   | M C/I |    |   | /I  |  |

|           |           |                |     | IN    |    |   |     | OUT   |    |   |     |  |

| 1         | 1         | 512            |     | B1    | B2 | М | C/I | B1    | B2 | М | C/I |  |

\* minimum BCLK values to have the channels as indicated.

#### V3..0: SYNCHRONOUS TE RATE SELECT, ASYNC TE INTERMEDIATE RATE SELECT

| V3 |   |   | Terminal Speed | Intermediate<br>Speed | Frame               | Repetition Coef. |   |  |

|----|---|---|----------------|-----------------------|---------------------|------------------|---|--|

| 0  | 0 | 0 | 0              | 64000 bps             | 64 kHz              | TRANSP.          | 1 |  |

| 0  | 0 | 0 | 1              | 600 bps               | 8 kHz               | 80               | 8 |  |

| 0  | 0 | 1 | 0              | 1200 bps              | 8 kHz               | 80               | 4 |  |

| 0  | 0 | 1 | 1              | 2400 bps              | 8 kHz               | 80               | 2 |  |

| 0  | 1 | 0 | 0              | 3600 bps**            | 8 kHz               | 80               | 1 |  |

| 0  | 1 | 0 | 1              | 4800 bps              | 8 kHz               | 80               | 1 |  |

| 0  | 1 | 1 | 0              | 7200 bps*             | 16 kHz              | 80               | 1 |  |

| 0  | 1 | 1 | 1              | 9600 bps              | 16 kHz              | 80               | 1 |  |

| 1  | 0 | 0 | 0              | 12000 bps*            | 32 kHz              | 80               | 1 |  |

| 1  | 0 | 0 | 1              | 14400 bps*            | 32 kHz              | 80               | 1 |  |

| 1  | 0 | 1 | 0              | 19200 bps             | 19200 bps 32 kHz 80 |                  | 1 |  |

| 1  | 0 | 1 | 1              | 38400 bps**           | 64 kHz              | 32               | 1 |  |

| 1  | 1 | 0 | 0              | 48000 bps             | 64 kHz              | 32               | 1 |  |

| 1  | 1 | 0 | 1              | 56000 bps             | 64 kHz              | 64               | 1 |  |

| 1  | 1 | 1 | 0              | 57600 bps**           | 64 kHz              | TRANSP.          | 1 |  |

| 1  | 1 | 1 | 1              | 64000 bps             | 64 kHz              | TRANSP.          | 1 |  |

\* For 7200/12000/14400 bauds Network Independent Clock is not supported even when programmed. "-" reserved.

\*\* Values not defined in ECMA 102/V110 recommendations.

# TEMIC MATRA MHS

# 29C93A

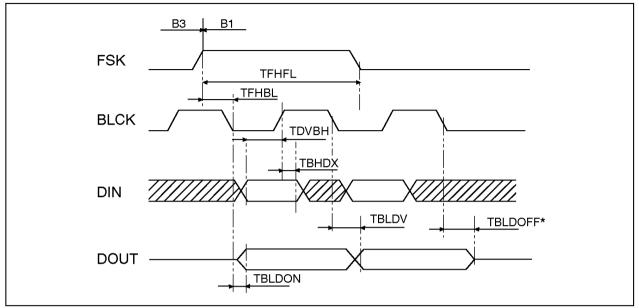

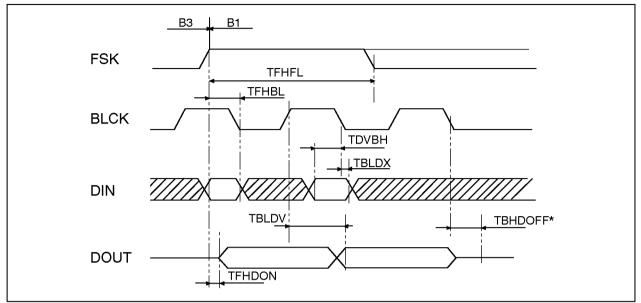

### c) IOM OPERATING MODE

d) SLD OPERATING MODE

#### CHANNEL DETAIL (to allow I460 multiplexing)

FSK

| ASCLK<br>MSB | ADI | DRESS = 04H | RESET = 40H/2 | 20H R/W | A | SYNCHRONOU | JS CLOCK PRO | GRAMMING F | REGISTER<br>LSB |  |

|--------------|-----|-------------|---------------|---------|---|------------|--------------|------------|-----------------|--|

|              |     | TRSEL       | RRSEL         | AR4     |   | AR3        | AR2          | AR1        | AR0             |  |

| TRSEL | RRSEL |                                                      |

|-------|-------|------------------------------------------------------|

| 0     | 0     | NOT USED                                             |

| 0     | 1     | Receive (remote to local) asynchronous rate select   |

| 1     | 0     | Transmit (local to remote) asynchronous rate select  |

| 1     | 1     | Same asynchronous rate on receive and transmit side. |

For write operation, if receive and transmit rates are different, the user should do two operations, one for each side. If both are the same, a single write is sufficient.

For read operation, TRSEL and RRSEL bits show which side (s) is (are) concerned.

AR4..AR0 Asynchronous rate selection

| AR4 | AR3 | AR2 | AR1 | AR0 | ASYNC. RATE |

|-----|-----|-----|-----|-----|-------------|

| 0   | 0   | 0   | 0   | 0   | 50 bps      |

| 0 0 |     | 0   | 0   | 1   | 75 bps      |

| 0   | 0 0 |     | 1   | 0   | 110 bps     |

| 0   | 0   | 0   | 1   | 1   | 150 bps     |

| 0   | 0   | 1   | 0   | 0   | 200 bps     |

| 0   | 0   | 1   | 0   | 1   | 300 bps     |

| 0   | 0   | 1   | 1   | 0   | 600 bps     |

| 0   | 0   | 1   | 1   | 1   | 1200 bps    |

| 0   | 1   | 0   | 0   | 0   | 2400 bps    |

| 0   | 1   | 0   | 0   | 1   | 3600 bps    |

| 0   | 1   | 0   | 1   | 0   | 4800 bps    |

| 0   | 1   | 0   | 1   | 1   | 7200 bps    |

| 0   | 1   | 1   | 0   | 0   | 9600 bps    |

| 0   | 1   | 1   | 0   | 1   | 12000 bps   |

| 0   | 1   | 1   | 1   | 0   | 14400 bps   |

| 0   | 1   | 1   | 1   | 1   | 19200 bps   |

| 1   | 0   | 0   | 0   | 0   | 38400 bps   |

| 1   | 0   | 0   | 0   | 1   | 57600 bps   |

**FASYNC** ADDRESS = 05H RESET = 00H MSB

ASYNCHRONOUS FORMAT REGISTER

LSB

| HO NS1 NS0 ND1 ND0 P2 P1 P0 | - |    |     |     |     |     |    |    |    |

|-----------------------------|---|----|-----|-----|-----|-----|----|----|----|

|                             |   | H0 | NS1 | NS0 | ND1 | ND0 | P/ | P1 | P0 |

R/W

#### H0: MCLK SELECT (BAUD RATE GENERATOR)

- 0 7.68 MHz clock select

- 1 12.288 MHz clock select

```